This post is an introduction to RISC-V instruction set architecture (ISA), explaining its particularities and potentials.

What is RISC-V?

An instruction set architecture (ISA) is part of the abstract model of a computer that defines how the CPU is controlled by the software. The ISA acts as an interface between the hardware and the software, specifying both what the processor is capable of doing as well as how it gets done.

An ISA adopts a specific computer architecture, for instance Complex Instruction Set Computer (CISC) or Reduced Instruction Set Computer (RISC).

An ISA is just an abstract definition that requires implementations based on it. Without implementations, the ISA would just be a theoretical architecture. Each chip manufacturer can develop its own implementation, that could be either proprietary or open.

In the 2020s decade, the most popular ISA families are x86 and arm, that are both proprietary. x86 are CISC ISAs owned by American companies Intel and AMD, and arm are RISC ISAs owned by American Arm Ltd. These companies develop ISAs and license them to other companies as a paid service.

RISC-V is an open standard RISC ISA, developed originally in the UC Berkeley and maintained by RISC-V International (that was initially known as RISC-V Foundation) since 2015. Unlike x86 and arm, RISC-V is and open standard so third companies do not need a paid license to use it.

RISC-V was originally released in 2014, and has become the industry standard for an open RISC ISA. An example of a less popular open RISC ISA is OpenRISC, that was released earlier in 2000.

The 32-bit version of RISC-V is codenamed as RV32, while the 64-bit is RV64.

Are there RISC-V Devices available in the Market?

As of 2023, RISC-V is not yet mainstream in the hardware or software industry. The industry is waiting that major manufactures adopt RISC-V to declare it a success.

First chip companies investing on RISC-V:

- Quintauris is a joint venture of Qualcomm and 4 other semiconductor companies focused on RISC-V hardware development.

- T-Head (Alibaba) builds chips like the T-head RVB-ICE Development Board Dual-core XuanTie C910 RISC-V.

First device companies investing on RISC-V:

- Chinese company Sipeed is starting to manufacture RISC-V devices and components. It created the RISC-V-based PDA MaixAmigo in 2021, while it is planning to release a RISC-V phone in 2024.

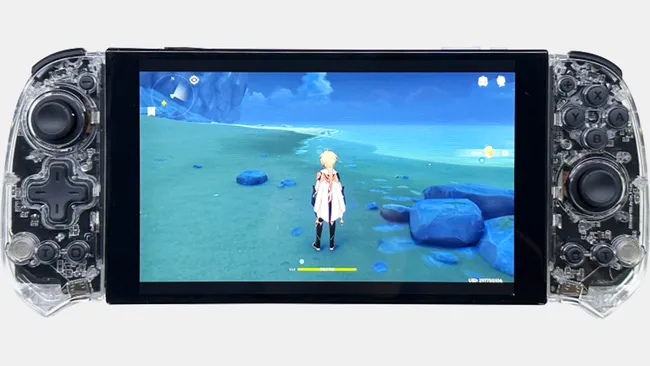

Sipeed’s Lichee Pocket 4A is the first announced RISC-V gameheld console, that is Debian Linux and Android compatible.

Take into account that the use of a open ISA does not mean that the computer components and firmware are open necessarily. Proprietary hardware and software can be built on top of the open ISA standard.

Can I run RISC-V Software without having RISC-V Hardware?

There is software available that allows to run a virtual RISC-V processor on a non-RISC-V processor. Some example are provided below.

OpenPiton is a Princeton University open project to provide multi-core processors. It is explained on the official web and on its code repository.

Ariane CPU is an open RISC-V CPU implementation that can be run on OpenPiton. You can find the repository on this external link.

The OpenPiton+Ariane technology enables the creation of a multi-core processor using the OpenPiton framework and incorporating multiple Ariane CPUs.

QEMU is a free and open source (FOSS) emulator that supports RISC-V, among other ISAs. You can find more information on the official website and its code repository.

Spike is a FOSS RISC-V simulator. You can find more information on the code repository.

Is there RISC-V Software?

RISC-V Software Ecosystem (RISE) is a Linux Foundation project to create software for RISC-V hardware, including OSs, toolchains and runtimes. It is backed by global industry leaders like Google, Intel, Nvidia and Qualcomm. You can find an overview of the available software on this on this external link.

OSs supporting RISC-V, as of 2024:

- Debian Linux (since 2018-2023)

- Android (since 2023)

- FreeBSD

- OpenBSD

The FOSS RISC-V GNU Toolchain includes tools to work with RISC-V, including the GCC compiler. You can find the code repository on this external link.

This support was provided before RISC-V hardware devices ever existed. It makes sense, as the hardware industry needs to have a reason to make a significant invest on this ISA and ensure that there are potential users prior to its development.

Why is RISC-V ISA relevant?

RISC-V has potential because it could become the first open ISA to be accepted mainstreamly by the hardware and software industry.

The idea of an open ISA is especially attractive for organizations and individuals belonging to these groups:

- Free and open source software (FOSS) supporters, who embrace open standards and systems

- SMEs of the industry that cannot afford ISA license costs

- Organizations that want to reduce risks and/or costs by being independent from the companies holding the ISA licenses

This third case would be relevant for Chinese companies that are trying to reduce their dependency on American tech companies, and avoid situations like the Huawei ban on collaboration with US companies by the US government.

What is the future of RISC-V?

A possible scenario is that the RISC-V adoption is pushed by Chinese technology companies, as they have actual incentives to avoid licensed architectures developed in the USA.

On the other hand, there are serious Western proposals to develop RISC-V chips and software, such as the Germany-based chip manufacturer Quintauris and software development RISE project.

The fact that prestigious OS developers like Debian Linux and Android are officially supporting RISC-V gives credibility to this ISA open alternative.

RISC-V Courses

The Linux Foundation offers some free courses about RISC-V:

- Introduction to RISC-V (LFD110x)

- Building a RISC-V CPU Core (LFD111x)

- Building Applications with RISC-V and FreeRTOS (LFD112x)

- RISC-V Toolchain and Compiler Optimization Techniques (LFD113x)

- Microcontroller Applications with RISC-V (LFD115x)

- Foundations of RISC-V Assembly Programming (LFD117x)

You might also be interested in…

External References

- RISC-V ecosystem

- Agam Shah; “RISC-V Finds Its Foothold in a Rapidly Evolving Processor Ecosystem“; The New Stack, 2023-06

- Matthew Connatser; “RISC-V hardware ecosystem gets strong industry support – Qualcomm joins with four other industry players to form Quintauris“, Tom’s Hardware, 2023-12-24

- RISC-V devices

- Sipeed MaixAmigo

- Sipeed; “MaixAmigo Wiki“; Sipeed

- Sipeed Liche Pocket 4A

- Sipeed; “Lichee Pocket 4A“; Sipeed

- Anton Shilov; “World’s first RISC-V handheld gaming system announced — retro gaming platform uses Linux“; Tom’s Hardware, 2023-12-20

- Sipeed MaixAmigo